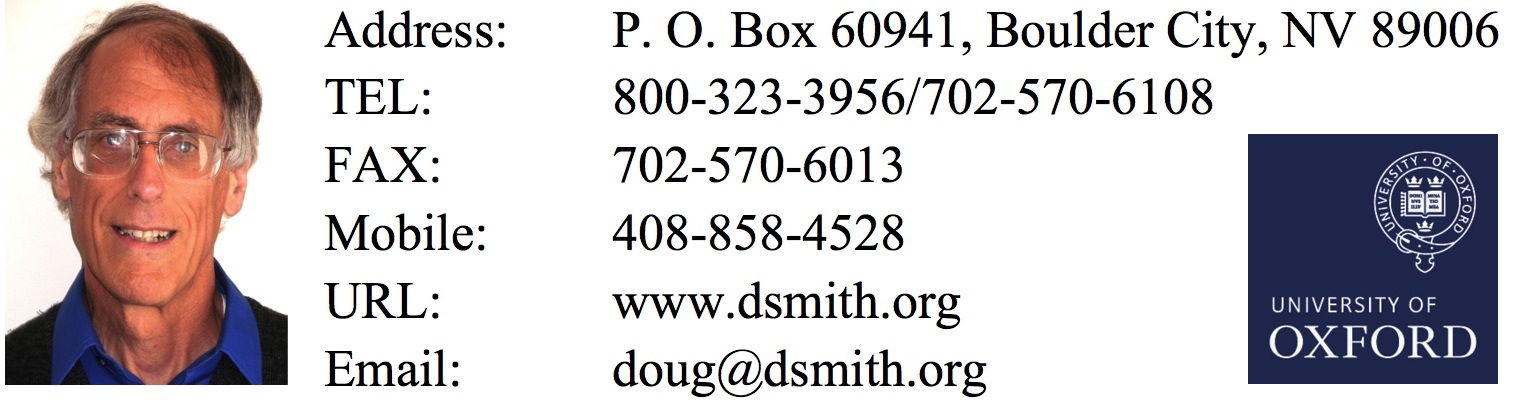

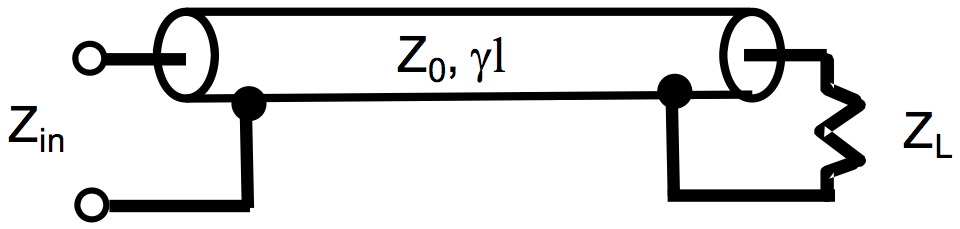

Figure 1. Transmission Line With Input and Load Impedances

Abstract: A new equivalent circuit for Zin of

an arbitrarily terminated transmission

line is presented, one which

employs only lumped impedances and

short and open line stubs in

series‐parallel combination. The new picture

readily illustrates concepts of line

matching and impedance inversion at quarter‐wave frequencies, and also offers insights into transient and off‐resonance response.

Discussion: Tim Maloney of

Intel Corporation has devised a simple, intuitive, and useful

equivalent circuit for a transmission line using shorted and open

transmission line segments and submitted it for publication on this

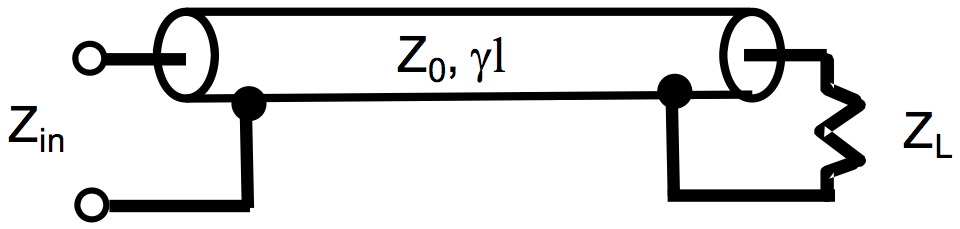

site. In essence, his equivalent circuit transforms the transmission

line of Figure 1 above into the configuration of Figure 2 below. This

is a very useful equivalent circuit.

To read Tim's paper in pdf format,

click here.

Don't be scared by the look of the equations you see on the page. Tim

does an excellent job of simplifying their interpretation into an easy

to understand concept.

Figure 2.Equivalent Circuit for Transmission Line With Input and Load Impedances

Summary: Tim

Maloney's paper on an equivalent circuit for transmission lines is an

intuitive and very useful treatment of transmission lines. Many

engineers will find this equivalent circuit useful in their work.

Tim Maloney's paper:

- Novel Equivalent Circuit for Zin of an Arbitrarily Terminated Transmission Line

Timothy J. Maloney, Intel Corporation

I am writing this from my new office in Boulder City, NV!!! I am doing morning 5 to 10 minute podcasts on

technical topics most mornings I am in the office. These podcasts will

appear on the home page of

http://CircuitAdvisor.com

by late morning except for days when I am not in the office. The first

one has been posted under the headings of Free Audio, General Interest.

Check

out my public seminar offering in Boulder City, NV. This is one of the

best seminar values around because the industry typical fee includes

more than just the seminar and lunch, but airport

transportation in NV, lodging in the historic Boulder City Dam Hotel and

Museum, and breakfast and lunch each day. Click here for more details.

If you like the information in this article and others on this website,

much more information is available in my courses.

Click here

to see a listing of upcoming courses on design, measurement, and

troubleshooting of chips, circuits, and systems.

Click here to see upcoming seminars in Boulder City, NV.

|

Our office, laboratory, and classrooms are located in the

----------

Historic Boulder City Dam Hotel and Museum

1305 Arizona Street, Boulder City, Nevada 89005

Phone: (702) 293-3510

----------

Come

for a technical seminar, design review/troubleshooting, or just for a

visit and mix a little history of the Old West with your work!

|

|

|

|

Our Silicon Valley associate office and lab are located at

----------

NASA-Ames Research Center

RMV Technology Group

Bldg. 19, Suite 1073, M/S 19-46C

Moffett Field, CA 94035

|

Need help with a design or additional training on technical subjects? Click on the image below to go to

CircuitAdvisor.com, a new engineering resource for training, news, and

fun.

Click here for a description of my

latest seminar titled (now also available online as a WebEx seminar):

EMC

Lab Techniques for Designers

(How to find EMC problems and have some

confidence your system will pass EMC testing while it is still in your

lab).

Top of page

Home