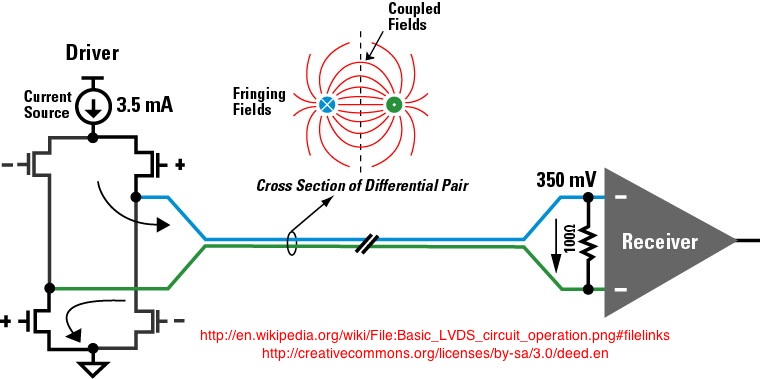

LVDS offers substantial benefits from the differential mode signaling

utilized. However, there are serious limitations with LVDS regarding

pulsed EMI such as ESD and EFT.

I have noticed a trend of problems with systems using LVDS over the

last several years. The problems result from the approximately two Volt

common mode range of LVDS. Once this limit is exceeded, the receiver

input saturates and the data is lost. Such a common mode voltage may be

generated by ESD and EFT under certain conditions including:

- Signals that leave the circuit board on which they are generated

- Signals that travel over long shielded cables (one meter or more,

for instance) or over any length of unshielded cables outside of a

shielded enclosure

- Single point grounding is attempted in the system design

- Some PCB stack-ups and layouts, such as traversing from an upper

layer referenced to a ground plane of a board with many layers, for

instance 16, to a lower layer referenced to a power plane unless

several other conditions are met

- The signals are generated or used on a four layer PCB, unless great care is taken in routing and grounding

If the receiver is likely to be driven into saturation by any cause, it

is necessary for the system to be tolerant of the errors that will be

generated in the data. If not, the system will likely experience

problems, especially when ESD and/or EFT is present either for an

intended test or in the operating environment of the equipment. Meeting

one or more of the conditions above does not guarantee a problem, but

there is a substantial risk of serious system problems if the system is

not error tolerant. A good rule of thumb for LVDS is to consider it as

two unbalanced signals with no common mode rejection as far as pulsed

EMI from sources like ESD and EFT are concerned.

Summary:

Differential signaling, such as LVDS, does not necessarily confer

immunity to EMI generated by pulsed sources like ESD and EFT. In fact,

problems are likely to occur under a set of PCB, cable, and enclosure

conditions that occur in many systems.