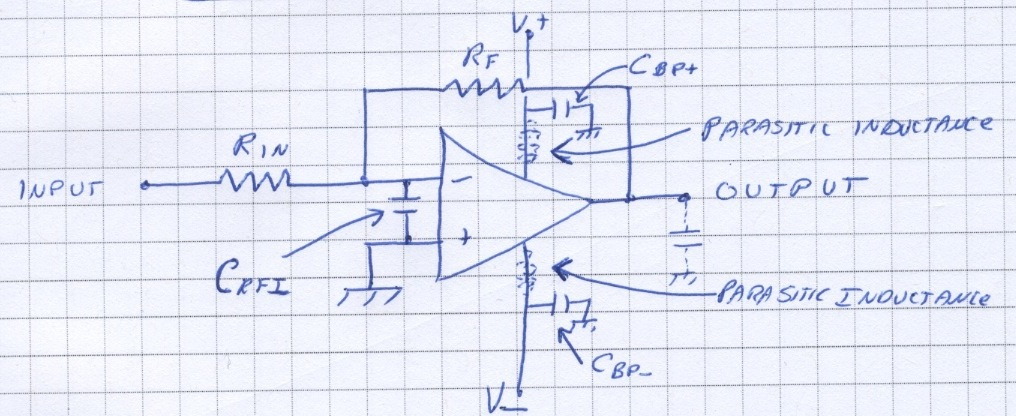

Figure 1 shows a typical inverting op

amp circuit with parasitic inductance in the power connections.

This inductance might be only a few tens of nanohenries and still cause

problems, even for low frequency 1 MHz unity gain bandwidth op amps. Also

shown in Figure 1 is the C

RFI capacitor described in the

November 2013 Technical Tidbit for increasing immunity to external EMI.

A problem occurs with inductance in the power leads because the

inductance essentially adds another feedback loop from the output to

the power pins, through the last stage or two of the op amp back to the

output. The bandwidth of this feedback loop can be much higher than the

bandwidth of the complete op amp. I have seen 1 MHz unity gain op amps

oscillate at frequencies of over 20 MHz in response to inductance in

the power leads!

This unwanted feedback loop occurs because driving current to the output causes drop across the power lead inductance which

then feeds high frequency energy into the power pins (essentially

another input). The op amp rejection of noise at the power pins is

generally very low or non-existent at 20X the unity gain frequency of

the op amp. Feeding capacitive loads can increase this effective feedback signal even further.

Many circuits utilizing 1 MHz unity gain op amps are constructed on

two layer PCBs to save costs as they are perceived to be low frequency

circuits, not needing the power and ground planes. Thus, the inductance

between the op amp power pins and the nearest bypass capacitor is

increased compared to multi-layer PCBs, aggravating the effect.

When designing op amp circuits, even low frequency ones, be sure to

provide bypass capacitors right at the power pins, making as small a

loop as possible between the + and - power pins.

Summary: Parasitic

inductance in the power leads of op amp circuits can cause oscillation

at frequencies well above the unity gain bandwidth of an op amp. Always

provide bypass capacitor(s) between the power pins as close as possible

to those pins to insure low parasitic inductance, even for low

frequency circuits.