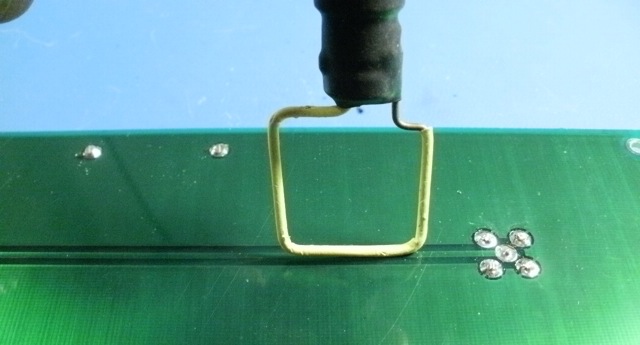

Figure 1. EFT Generated by a Power Supply

Vertical = 1 Amp/div, Horizontal = 1usec/div

Abstract: ESD problems at the system level can be difficult to track down. This article links my

paper written for the

Institute of Physics Electrostatics Symposium in

Southampton, England in April 2015 on ESD troubleshooting at the system level which can simplify the process.

Figure 1 shows injecting pulsed noise inductively into a PCB trace,

one of the techniques described in the paper along with several

techniques including capacitive coupling of noise into cables and high

pass filtering of the ESD simulator current waveform.

My Institute of Physics paper "Techniques for Investigating the

Effects of ESD on Electronic Equipment," is available on this website, click here

to view or download a copy.

NEW: Click here,

to see descriptions and registration information on my one hour

webinars than can solve difficult design problems quickly. Touching on

topics like signal integrity, EMC, ESD, and general analog and digital

design, these webinars are a quick way to get your design working.

There are public presentations every week as well as private

presentations on demand for as low as $40/person. New webinars are

added periodically.

Check

out my public seminar offering in Boulder City, NV. This is one of the

best seminar values around because the industry typical fee includes

more than just the seminar and lunch. It includes airport

transportation in NV, lodging in the historic Boulder City Dam Hotel and

Museum, and breakfast and lunch each day. Click here for more details.

The combination of the material presented, the venue, and the

passionate presentation will likely make for the best technical short

course/seminar you have ever taken! Didn't think a technical

presentation can be passionate,? This one is. The result is this short

course/seminar will likely be the most informative, practical, and FUN

seminar you can attend.

If you like the information in this article and others on this website,

much more information is available in my courses.

Click here

to see a listing of upcoming courses on design, measurement, and

troubleshooting of chips, circuits, and systems.

Click here to see upcoming seminars in Boulder City, NV.

|

Our office, laboratory, and classrooms are located in the

----------

Historic Boulder City Dam Hotel and Museum

1305 Arizona Street, Boulder City, Nevada 89005

Phone: (702) 293-3510

----------

Come

for a technical seminar, design review/troubleshooting, or just for a

visit and mix a little history of the Old West with your work!

|

|

|

|

Our Silicon Valley associate office and lab are located at

----------

NASA-Ames Research Center: RMV Technology Group

Bldg. 19, Suite 1073, M/S 19-46C

Moffett Field, CA 94035

http://esdrmv.com

Phone: (650) 964-4792

----------

RMV is a materials/ESD lab serving NASA and commercial customers.

|

Need help with a design or additional training on technical subjects? Click on the image below to go to

CircuitAdvisor.com, an engineering resource for training, news, and

fun. The site is being reorganized for group memberships and should be back up soon.

Click here for a description of one of my seminars titled (now also available online as a WebEx seminar):

EMC

Lab Techniques for Designers

(How to find EMC problems and have some

confidence your system will pass EMC testing while it is still in your

lab).

Top of page

Home